Купете BGA Rework Station

1. Можете да закупите BGA Rework Station директно от оригиналния производител.2. DH-A2 Автоматична BGA преработваща станция.3. Микрометър за регулиране на ъгъла на BGA и регулиране на дънната платка.4. Пристанище: Шенжен.

Описание

Купете BGA Rework Station

1. Приложение на автоматична оптична BGA преработваща станция

Работа с всички видове дънни платки или PCBA.

Запояване, reball, разпояване на различни видове чипове: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP,

PBGA, CPGA, LED чип.

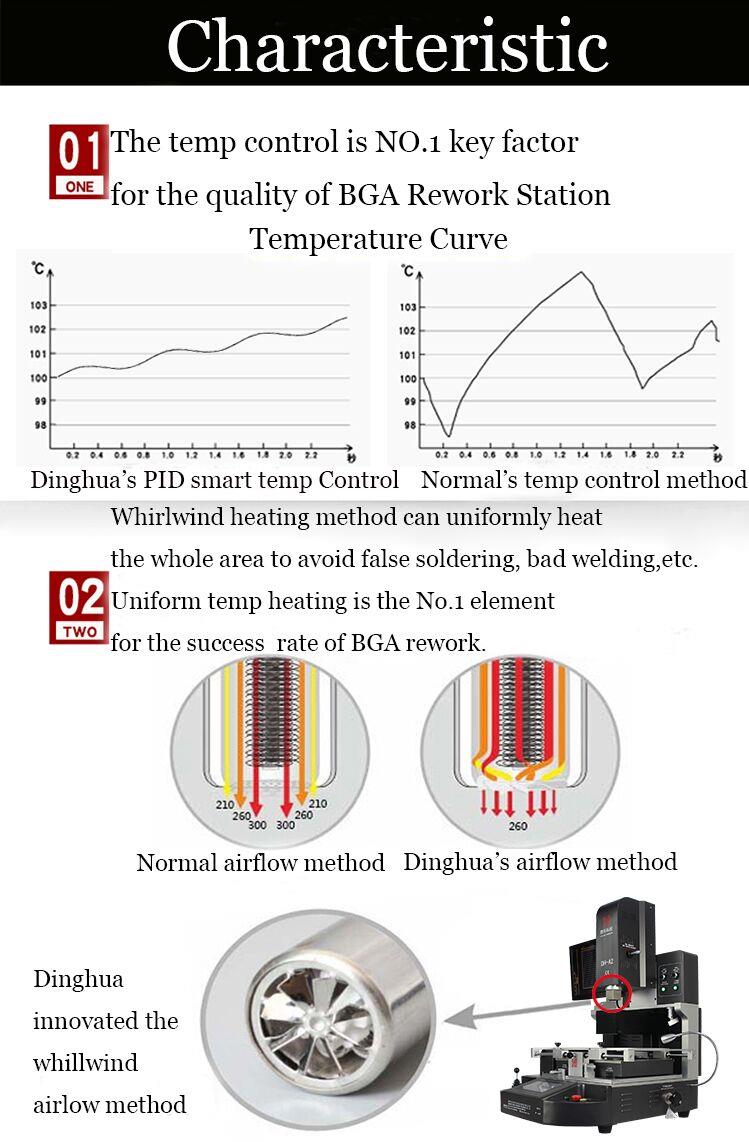

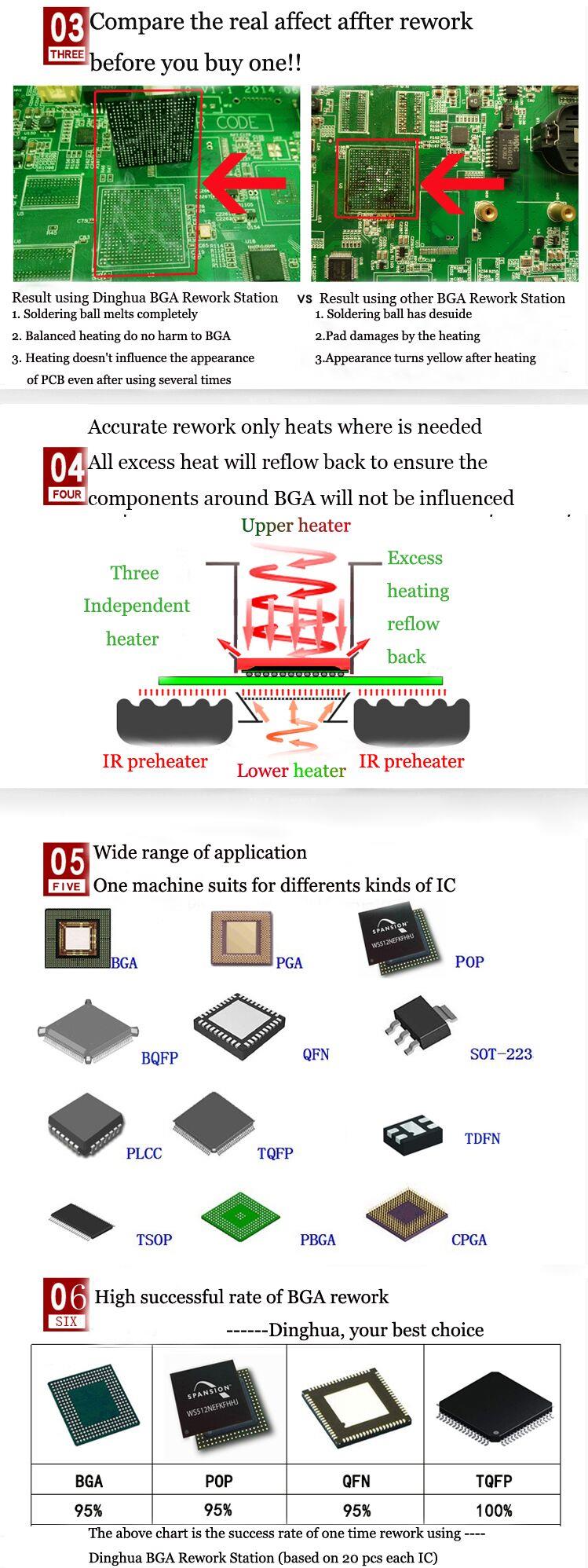

2. Характеристики на продукта наАвтоматичен оптиченBGA Rework Station

3.Спецификация наАвтоматичен оптиченBGA Rework Station

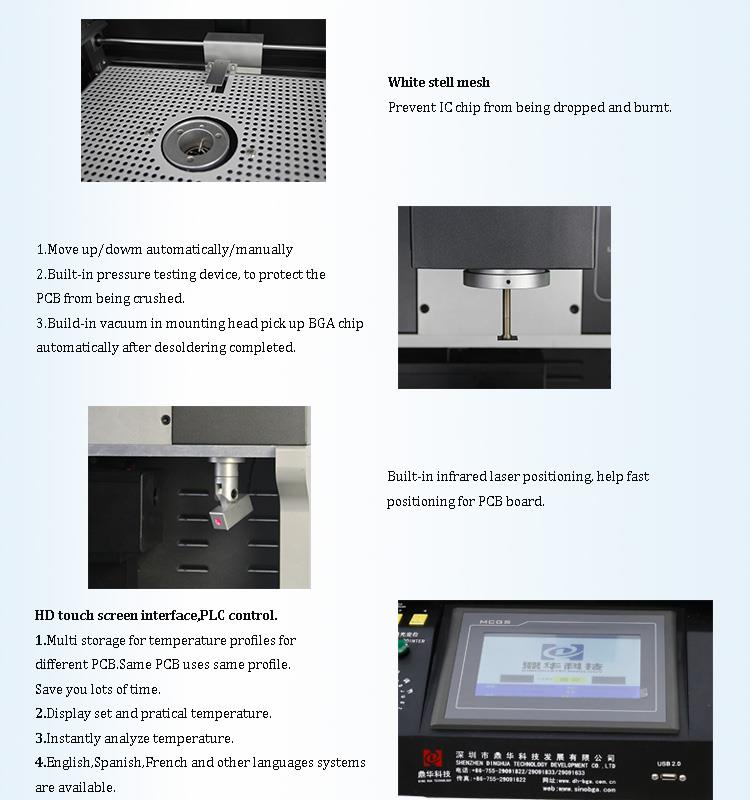

4.Подробности заАвтоматичен оптиченBGA Rework Station

5. Защо да изберете нашияАвтоматичен оптиченBGA Rework Station?

6.Удостоверение заАвтоматичен оптиченBGA Rework Station

Сертификати UL, E-MARK, CCC, FCC, CE ROHS. Междувременно, за подобряване и усъвършенстване на системата за качество,

Dinghua е преминал сертификат за одит на място по ISO, GMP, FCCA, C-TPAT.

7.Опаковане и изпращане наАвтоматиченBGA Rework Station

8.Пратка заАвтоматичен оптиченBGA машина за реболинг

DHL/TNT/FEDEX. Ако искате друг срок за доставка, моля, кажете ни. Ние ще ви подкрепим.

9. Условия на плащане

Банков превод, Western Union, кредитна карта.

Моля, кажете ни, ако имате нужда от друга поддръжка.

10. Как работи автоматичната BGA IC машина за реболиране DH-A2?

11. Свързани знания

Относно флаш чипа

Динамика на предлагането

Наскоро новият собственик на компанията за чипове на SandForce LSI каза, че разработва нов фърмуер за SF master SSD

в Ultrabook. Основната функция е да намали консумацията на енергия на SSD, както и да подобри производителността на

SSD и ускорете стартирането. скорост.

параметър

3. 3V захранване;

Масивът на клетките на вътрешната памет на чипа е (256M + 8.192M) бита × 8 бита, а регистърът на данните и буферната памет са

(2k + 64) бита × 8 бита;

I/O порт с мултиплексиране на инструкции/адреси/данни;

Командите за програмиране и изтриване могат да бъдат спрени по време на преобразуване на мощността;

Благодарение на надеждната CMOS подвижна технология, чипът може да постигне максимум 100kB цикъл на програма/изтриване, което

гарантира съхранение на данни за 10 години без загуба.

Работен статус

I/O0~I/O7: порт за вход и изход на данни, I/O порт често се използва за въвеждане на инструкция и адрес и вход/изход на данни,

където са данните

Въведете по време на процеса на четене. Когато чипът не е избран или не може да бъде изведен, I/O портът е в състояние на висок импеданс.

CLE: Резето на инструкцията се използва за активиране на инструкцията към пътеката на регистъра на инструкциите и фиксиране на инструкцията на

нарастващият ръб на WE и CLE е висок.

ALE: Резе на адреса, използвано за активиране на пътя на адреса към вътрешния адресен регистър и адресът се заключва на

нарастващият ръб на WE и ALE е висок.

CE: Селектор на чипове, използван за управление на избора на устройство. Когато устройството е заето, CE е висок и се игнорира и устройството не може да се върне

към състояние на готовност.

RE: Разрешение за четене, използвано за контролиране на непрекъснатия изход на данни и изпращане на данните към I/O шината. Изходните данни са валидни само за

падащия ръб на RE и може също да натрупва вътрешни адреси на данни.

WE: Терминалът за разрешаване на запис се използва за управление на писането на инструкции на I/O порта. В същото време командата адрес

и данните могат да бъдат фиксирани по нарастващия фронт на WE импулса през този порт.

WP: Защита срещу запис, която може да бъде защитена от запис при преобразуване на мощност през WP терминала. Когато WP е нисък, той е вътрешен

генераторът на високо ниво ще бъде нулиран.

R/B : Изход за готовност/заето, изходът на R/B може да покаже работния статус на устройството. Когато R/B е нисък, това показва, че програма,

се извършва операция по изтриване или произволно четене. След като операцията приключи, R/B автоматично ще се върне на високо ниво. Тъй като

терминалът е изход с отворен дрейн, той няма да бъде в състояние с висок импеданс дори когато чипът не е избран или изходът е деактивиран.

PRE: Операция за четене при включване, използвана за управление на операцията за автоматично четене, когато захранването е включено, и терминалът PRE може да бъде свързан

към VCC, за да реализирате операцията за автоматично четене при включване.

VCC: Терминал за захранване на чип.

VSS: Заземяване на чипа.

NC: Висящи.

Редактиране на работния статус

Операция за четене на 1 страница

Състоянието по подразбиране на флаш чипа е състояние на четене. Операцията за четене е да стартирате инструкцията, като напишете 00h адреса на

регистър на инструкции през 4 цикъла на адресиране. След като инструкцията бъде заключена, операцията за четене не може да бъде записана на следващата страница.

Данните могат да бъдат произволно изведени от една страница чрез написване на инструкция за извеждане на произволни данни. Адресът на данните може да се намери автоматично

следващия адрес чрез произволни инструкции за извеждане от адреса на данните, който трябва да бъде изведен. Операциите за извеждане на произволни данни могат да се използват многократно

пъти.

Програмиране на 2 страници

Програмирането на флаш чипа е страница по страница, но той поддържа многократно частично програмиране на страници в цикъл на програмиране на една страница,

докато броят на последователните страници на частична страница е 2112. Операцията на програмата може да бъде стартирана чрез писане в програмата за страници

инструкция за потвърждение (10h), но непрекъснатите данни трябва да бъдат въведени преди инструкцията (10h) да бъде написана.

Непрекъснато зареждане на данни След като напишете инструкция за непрекъснато въвеждане на данни (80h), тя ще започне 4 цикъла на въвеждане на адрес и зареждане на данни, но

думата е различна от програмираните данни, не е необходимо да се зарежда. Чипът поддържа произволно въвеждане на данни в страницата и може

автоматично променя адреса според командата за произволно въвеждане на данни (85h). Произволното въвеждане на данни също може да се използва многократно.

3 програмиране на кеша

Програмирането на кеша е вид програмиране на страници, което може да се извърши от 2112-байтов регистър с данни и е валидно само в един блок. защото

флаш чипът има буфер за страници, той може да извършва непрекъснато въвеждане на данни, когато регистърът на данните е програмиран в клетката с памет. Кеш памет

програмирането може да започне само след края на непълен цикъл на програмиране и регистрите на данни се предават от кеша. Вътрешното програмиране може да се прецени по R/B щифта. Ако системата използва само R/B за наблюдение на напредъка на програмата, тогава редът на последната страница

на целевата програма трябва да бъдат подредени от инструкциите за програмиране на текущата страница.

4 единици за съхранение презапис

Този ефект може бързо и ефективно да презапише данните в страница без достъп до външната памет. Тъй като времето, прекарано на непрекъснато

достъпът и презареждането са съкратени, възможността за изпълнение на системата е подобрена. Особено когато част от блока е надстроена и

останалата част от блока трябва да се копира в новия блок, неговите предимства са ясно показани. Тази операция е непрекъснато изпълнявана команда за четене,

но не изисква непрекъснат достъп до и копиране на програмата от адреса на местоназначение. Операция за четене на адреса на оригиналната страница

Инструкцията на "35h" може да прехвърли всичките 2112 байта данни към вътрешния буфер за данни. Когато чипът се върне в състояние на готовност, страницата се копира

записва се инструкция за въвеждане на данни с цикъл на адреса на местоназначението. Програмата за грешка в тази операция се дава от статуса "успешен/неуспешен". Въпреки това,

ако операцията отнеме твърде много време за изпълнение, ще се получи битова грешка поради загуба на данни, което води до външна грешка "проверка/коригиране" проверка на устройството

провал. Поради тази причина операцията трябва да бъде коригирана с две грешки.

5 блок изтриване

Операцията по изтриване на флаш чипа се извършва на блокова основа. Зареждането на адрес на блок ще започне с инструкция за изтриване на блок и ще завърши в два цикъла. Всъщност, когато адресните редове A12 до A17 са оставени плаващи, само адресните редове A18 до A28 са налични. Изтриването може да започне чрез зареждане на командата за потвърждение на изтриването и адреса на блока. Тази операция трябва да се извърши в този ред, за да се предотврати влиянието на съдържанието на паметта от външен шум и причиняване на грешка при изтриване.

6 прочетено състояние

Регистър на състоянието във флаш чипа потвърждава, че операциите по програмиране и изтриване са завършени успешно. След инструкцията за запис (70h) в регистъра на инструкциите, цикълът на четене извежда съдържанието на регистъра на състоянието към I/O на падащия фронт на CE или RE. Регистърът на инструкциите ще остане в състояние на четене, докато пристигне новата инструкция, така че ако регистърът на състоянието е в състояние на четене по време на произволен цикъл на четене, тогава трябва да се даде инструкция за четене преди началото на цикъла на четене.